CN111355549B - Data protection method and device - Google Patents

Data protection method and device Download PDFInfo

- Publication number

- CN111355549B CN111355549B CN201811573811.5A CN201811573811A CN111355549B CN 111355549 B CN111355549 B CN 111355549B CN 201811573811 A CN201811573811 A CN 201811573811A CN 111355549 B CN111355549 B CN 111355549B

- Authority

- CN

- China

- Prior art keywords

- data packets

- channel

- read

- channels

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims abstract description 24

- 230000001960 triggered effect Effects 0.000 claims description 2

- 230000005540 biological transmission Effects 0.000 abstract description 6

- 238000005516 engineering process Methods 0.000 description 7

- 125000004122 cyclic group Chemical group 0.000 description 6

- 230000003287 optical effect Effects 0.000 description 6

- 238000004891 communication Methods 0.000 description 4

- 238000010586 diagram Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 2

- 239000008187 granular material Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 230000007723 transport mechanism Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0635—Clock or time synchronisation in a network

- H04J3/0638—Clock or time synchronisation among nodes; Internode synchronisation

- H04J3/0647—Synchronisation among TDM nodes

- H04J3/065—Synchronisation among TDM nodes using timestamps

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0635—Clock or time synchronisation in a network

- H04J3/0638—Clock or time synchronisation among nodes; Internode synchronisation

- H04J3/0658—Clock or time synchronisation among packet nodes

- H04J3/0661—Clock or time synchronisation among packet nodes using timestamps

- H04J3/0664—Clock or time synchronisation among packet nodes using timestamps unidirectional timestamps

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0635—Clock or time synchronisation in a network

- H04J3/0685—Clock or time synchronisation in a node; Intranode synchronisation

- H04J3/0691—Synchronisation in a TDM node

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0635—Clock or time synchronisation in a network

- H04J3/0685—Clock or time synchronisation in a node; Intranode synchronisation

- H04J3/0697—Synchronisation in a packet node

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L47/00—Traffic control in data switching networks

- H04L47/50—Queue scheduling

- H04L47/56—Queue scheduling implementing delay-aware scheduling

- H04L47/562—Attaching a time tag to queues

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Data Exchanges In Wide-Area Networks (AREA)

Abstract

本文公开了一种数据保护方法及装置。所述数据保护方法包括:源端单板为原始数据包添加时间戳,并通过两个通道将添加时间戳后的数据包并行发送至宿端单板;宿端单板在两个通道并行接收数据包,根据所述数据包携带的时间戳确定写入每一个通道的缓存队列的数据包并将所述数据包分别写入每一个通道的缓存队列中;宿端单板从两个通道的缓存队列中并行读取数据包,根据所述数据包携带的时间戳对两个通道读取的数据包进行对齐处理;宿端单板在对两个通道的读缓存操作对齐成功后,将从任意一个通道的缓存队列中读取的数据包进行输出。本文的技术方案能够提高数据包的传输可靠性。

This paper discloses a data protection method and device. The data protection method includes: the source-end single board adds a time stamp to the original data packet, and sends the time-stamped data packet to the sink-end single board in parallel through two channels; data packet, determine the data packet written into the buffer queue of each channel according to the time stamp carried by the data packet, and write the data packet into the buffer queue of each channel respectively; The data packets are read in parallel in the buffer queue, and the data packets read by the two channels are aligned according to the timestamps carried by the data packets; The data packets read in the buffer queue of any channel are output. The technical solution in this paper can improve the transmission reliability of data packets.

Description

技术领域technical field

本发明涉及光传输网技术领域,尤其涉及的是一种数据保护方法及装置。The present invention relates to the technical field of optical transmission network, in particular to a data protection method and device.

背景技术Background technique

OTN(Optical Transport Network,光传输网)的下背板交换,能够集OTN与分组交换于同一平台,可为运营商在网络设计和成本优化方面提供最大的灵活性,可以通过SA(Switch Access,交换接入)接口完成TDM(Time Division Multiplexing,时分复用)包交换。The lower backplane switching of OTN (Optical Transport Network, Optical Transport Network) can integrate OTN and packet switching on the same platform, which can provide operators with maximum flexibility in network design and cost optimization. Switch access) interface to complete TDM (Time Division Multiplexing, time division multiplexing) packet switching.

NP(Network Processor,网络处理器)对接下的包交换是通过以太网包的交换实现的,接口只能采用Interlaken接口实现。POTN(Packet Optical Transport Network,分组光传输网)技术是基于OTN技术上的具有分组交换和传输能力的一种技术,它主要是将PTN(Packet Transport Network,分组传送网)和OTN、分组、TDM、包交换等全部优势集中到同一个设备中,实现多颗粒的交换,对多种技术进行深层次的融合达到完美,其中的交叉板需要采用Interlaken接口实现交叉。The packet exchange under the connection of NP (Network Processor, network processor) is realized through the exchange of Ethernet packets, and the interface can only be realized by the Interlaken interface. POTN (Packet Optical Transport Network, Packet Optical Transport Network) technology is a technology based on OTN technology with packet switching and transmission capabilities. It mainly combines PTN (Packet Transport Network, Packet Transport Network) with OTN, packet, TDM All advantages such as , packet switching, etc. are concentrated in the same device to realize multi-granule switching and achieve perfect integration of multiple technologies. The cross-connect board needs to use the Interlaken interface to realize cross-connection.

但是在5G前传网络中,对TDM包的交换传输延时性能、传输数据可靠性提出了更高的要求。However, in the 5G fronthaul network, higher requirements are put forward for the switching and transmission delay performance of TDM packets and the reliability of transmitted data.

发明内容Contents of the invention

本发明所要解决的技术问题是提供一种数据保护方法及装置,能够提高数据传输的可靠性。The technical problem to be solved by the present invention is to provide a data protection method and device, which can improve the reliability of data transmission.

根据本申请的第一方面,本发明实施例提供了一种数据保护方法,包括:According to the first aspect of the present application, an embodiment of the present invention provides a data protection method, including:

源端单板为原始数据包添加时间戳,并通过两个通道将添加时间戳后的数据包并行发送至宿端单板;The source board adds a timestamp to the original data packet, and sends the time-stamped data packet to the sink board in parallel through two channels;

宿端单板在两个通道并行接收数据包,根据所述数据包携带的时间戳确定写入每一个通道的缓存队列的数据包并将所述数据包分别写入每一个通道的缓存队列中;The sink board receives data packets in two channels in parallel, determines the data packets to be written into the buffer queue of each channel according to the timestamp carried by the data packets, and writes the data packets into the buffer queue of each channel respectively ;

宿端单板从两个通道的缓存队列中并行读取数据包,根据所述数据包携带的时间戳对两个通道读取的数据包进行对齐处理;The sink board reads data packets in parallel from the buffer queues of the two channels, and performs alignment processing on the data packets read by the two channels according to the timestamps carried by the data packets;

宿端单板在对两个通道的读缓存操作对齐成功后,将从任意一个通道的缓存队列中读取的数据包进行输出。After the read cache operations of the two channels are successfully aligned, the sink board outputs the data packets read from the cache queue of any channel.

根据本申请的第二方面,本发明实施例提供了一种数据保护装置,包括:According to the second aspect of the present application, an embodiment of the present invention provides a data protection device, including:

源端单板处理模块,用于为原始数据包添加时间戳,并通过两个通道将添加时间戳后的数据包并行发送至宿端单板;The source-end single-board processing module is used to add a time stamp to the original data packet, and send the time-stamped data packet to the sink-end single board in parallel through two channels;

宿端单板处理模块,用于在两个通道并行接收数据包,根据所述数据包携带的时间戳确定写入每一个通道的缓存队列的数据包并将所述数据包分别写入每一个通道的缓存队列中,从两个通道的缓存队列中并行读取数据包,根据所述数据包携带的时间戳对两个通道读取的数据包进行对齐处理,在对两个通道的读缓存操作对齐成功后,将从任意一个通道的缓存队列中读取的数据包进行输出。The sink-end single-board processing module is configured to receive data packets in two channels in parallel, determine the data packets written into the buffer queue of each channel according to the timestamp carried by the data packets, and write the data packets into each In the buffer queue of the channel, data packets are read in parallel from the buffer queues of the two channels, and the data packets read by the two channels are aligned according to the timestamps carried by the data packets. After the operation is aligned successfully, the data packets read from the buffer queue of any channel are output.

与相关技术相比,本发明实施例提供的一种数据保护方法及装置,源端单板为原始数据包添加时间戳,并通过两个通道将添加时间戳后的数据包并行发送至宿端单板;宿端单板在两个通道并行接收数据包,根据所述数据包携带的时间戳确定写入每一个通道的缓存队列的数据包并将所述数据包分别写入每一个通道的缓存队列中,从两个通道的缓存队列中并行读取数据包,根据所述数据包携带的时间戳对两个通道读取的数据包进行对齐处理,在对两个通道的读缓存操作对齐成功后,将从任意一个通道的缓存队列中读取的数据包进行输出。本发明实施例的技术方案能够提高数据传输的可靠性。Compared with related technologies, in the data protection method and device provided by the embodiment of the present invention, the single board at the source end adds a time stamp to the original data packet, and sends the time-stamped data packet to the sink end in parallel through two channels single board; the sink-end single board receives data packets in two channels in parallel, determines the data packets written into the cache queue of each channel according to the timestamp carried by the data packets, and writes the data packets into the buffer queue of each channel respectively In the cache queue, data packets are read in parallel from the cache queues of the two channels, and the data packets read by the two channels are aligned according to the timestamps carried by the data packets, and the read cache operation of the two channels is aligned After success, output the data packets read from the buffer queue of any channel. The technical solutions of the embodiments of the present invention can improve the reliability of data transmission.

附图说明Description of drawings

图1为本发明实施例的一种数据保护方法流程图;FIG. 1 is a flowchart of a data protection method according to an embodiment of the present invention;

图2为本发明实施例的一种TDM包中携带时间戳的示意图;FIG. 2 is a schematic diagram of a time stamp carried in a TDM packet according to an embodiment of the present invention;

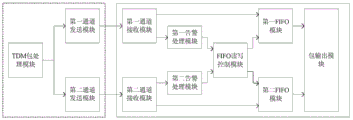

图3为本发明实施例的一种数据保护装置示意图;FIG. 3 is a schematic diagram of a data protection device according to an embodiment of the present invention;

图4为本发明示例1的一种数据保护装置示意图。FIG. 4 is a schematic diagram of a data protection device in Example 1 of the present invention.

具体实施方式Detailed ways

为使本发明的目的、技术方案和优点更加清楚明白,下文中将结合附图对本发明的实施例进行详细说明。需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互任意组合。In order to make the purpose, technical solution and advantages of the present invention more clear, the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined arbitrarily with each other.

实施例1Example 1

如图1所示,本发明实施例提供了一种数据保护方法,包括:As shown in Figure 1, an embodiment of the present invention provides a data protection method, including:

步骤S110,源端单板为原始数据包添加时间戳,并通过两个通道将添加时间戳后的数据包并行发送至宿端单板;Step S110, the source board adds a timestamp to the original data packet, and sends the time-stamped data packet to the sink board in parallel through two channels;

步骤S120,宿端单板在两个通道并行接收数据包,根据所述数据包携带的时间戳确定写入每一个通道的缓存队列的数据包并将所述数据包分别写入每一个通道的缓存队列中;In step S120, the sink board receives data packets in two channels in parallel, determines the data packets to be written into the cache queue of each channel according to the timestamp carried by the data packets, and writes the data packets into the buffer queue of each channel respectively. in the buffer queue;

步骤S130,宿端单板从两个通道的缓存队列中并行读取数据包,根据所述数据包携带的时间戳对两个通道读取的数据包进行对齐处理;Step S130, the sink board reads data packets in parallel from the buffer queues of the two channels, and performs alignment processing on the data packets read by the two channels according to the timestamps carried by the data packets;

步骤S140,宿端单板在对两个通道的读缓存操作对齐成功后,将从任意一个通道的缓存队列中读取的数据包进行输出;Step S140, after the read buffer operation of the two channels is successfully aligned, the sink board outputs the data packets read from the buffer queue of any channel;

在上述实施方式中,源端单板通过在原始数据包中添加时间戳为宿端单板的并行接收提供了数据对齐的参考依据。宿端单板在两个通道并行接收数据包,根据所述数据包携带的时间戳对写缓存和读缓存的操作进行控制。在读缓存时,通过检查两个通道读取的数据包携带的时间戳是否相同可以判断两个通道读出的数据包是否对齐。当两个通道的读操作对齐后,任意一个通道可以作为当前的工作通道,另一个通道可以作为备用通道。当工作通道发生故障时,由于两个通道读取的数据是一致的,因此可以达到无缝切换工作通道和备用通道,从而满足5G前传网络对通信延时和可靠性的苛刻要求。In the foregoing implementation manners, the source board provides a reference basis for data alignment for parallel reception of the sink board by adding a time stamp to the original data packet. The sink board receives data packets in two channels in parallel, and controls operations of the write cache and the read cache according to the time stamps carried in the data packets. When reading the cache, it can be judged whether the data packets read by the two channels are aligned by checking whether the time stamps carried by the data packets read by the two channels are the same. When the read operations of the two channels are aligned, any one channel can be used as the current working channel, and the other channel can be used as the standby channel. When the working channel fails, since the data read by the two channels is consistent, seamless switching between the working channel and the backup channel can be achieved, thereby meeting the stringent requirements of the 5G fronthaul network for communication delay and reliability.

在一种实施方式中,所述数据包包括:时分复用TDM数据包;In one embodiment, the data packet includes: a time division multiplexed TDM data packet;

在一种实施方式中,所述为原始数据包添加时间戳,包括:在TDM数据包的包头添加时间戳;In one embodiment, adding a time stamp to the original data packet includes: adding a time stamp to the header of the TDM data packet;

其中,如图2所示,TDM数据包包括:包头和负载;其中,包头包括16比特的时间戳和16比特的OH(Overhead,开销);Wherein, as shown in Figure 2, the TDM data packet includes: header and load; Wherein, header includes 16-bit timestamp and 16-bit OH (Overhead, overhead);

在一种实施方式中,所述两个通道均为Interlaken通道;其中,Interlaken是一种高速通道化的接口协议;In one embodiment, the two channels are Interlaken channels; wherein, Interlaken is a high-speed channelized interface protocol;

在一种实施方式中,所述根据所述数据包携带的时间戳确定写入每一个通道的缓存队列的数据包并将所述数据包分别写入每一个通道的缓存队列中,包括:In one embodiment, the determining the data packet written into the buffer queue of each channel according to the timestamp carried by the data packet and writing the data packet into the buffer queue of each channel respectively includes:

针对每一个通道,当所述通道接收到的数据包的时间戳从最大值变为最小值时,将接收携带所述最小值时间戳的数据包的时刻作为参考时刻,将在所述参考时刻之前接收的所有数据包写入该通道的缓存队列中;For each channel, when the time stamp of the data packet received by the channel changes from the maximum value to the minimum value, the time when the data packet carrying the time stamp of the minimum value is received is taken as the reference time, and at the reference time All previously received data packets are written into the buffer queue of the channel;

在一种实施方式中,所述根据所述数据包携带的时间戳对两个通道读取的数据包进行对齐处理,包括:In one embodiment, the alignment processing of the data packets read by the two channels according to the timestamps carried by the data packets includes:

当两个通道的缓存队列中允许读取的数据包的数量均达到或超过读取阈值时,同时读取两个通道的缓存队列,当从两个通道的缓存队列中读取的前n个数据包携带的时间戳相同时,确定两个通道读取的数据包对齐;When the number of data packets allowed to be read in the buffer queues of the two channels reaches or exceeds the read threshold, the buffer queues of the two channels are read at the same time. When the first n data packets read from the buffer queues of the two channels When the timestamps carried by the data packets are the same, it is determined that the data packets read by the two channels are aligned;

其中,n可以取值为1,或2或3或其他数值;Wherein, n can take a value of 1, or 2 or 3 or other values;

在一种实施方式中,所述根据所述数据包携带的时间戳对两个通道读取的数据包进行对齐处理,还包括:In one embodiment, the alignment processing of the data packets read by the two channels according to the timestamps carried by the data packets further includes:

当一个通道的缓存队列中允许读取的数据包的数量达到或超过读取阈值,而另一个通道的缓存队列中允许读取的数据包的数量为零时,确定两个通道的读缓存操作不满足对齐条件;Determines read caching operations for both channels when the number of read-allowed packets in one channel's cache queue meets or exceeds the read threshold, while the other channel's cache queue has zero allowed-read packets The alignment condition is not met;

在一种实施方式中,所述根据所述数据包携带的时间戳确定写入每一个通道的缓存队列的数据包并将所述数据包分别写入每一个通道的缓存队列中,包括:In one embodiment, the determining the data packet written into the buffer queue of each channel according to the timestamp carried by the data packet and writing the data packet into the buffer queue of each channel respectively includes:

查询每一个通道的告警信息;Query the alarm information of each channel;

对任意一个通道,在未查询到所述通道的告警信息时,触发对所述通道的写缓存处理;For any channel, when the alarm information of the channel is not queried, trigger the write cache processing of the channel;

在一种实施方式中,查询每一个通道的告警信息后,所述方法还包括:In one embodiment, after querying the alarm information of each channel, the method further includes:

在查询到任意一个通道的告警信息后,对所述告警信息进行处理;After querying the alarm information of any channel, processing the alarm information;

所述告警信息包括以下至少一种:Interlaken通道未对齐、去偏移失败、CRC(Cyclic Redundancy Check,循环冗余校验)校验错误、包头和包尾不匹配错误、和元帧长度错误;The alarm information includes at least one of the following: Interlaken channel misalignment, de-skew failure, CRC (Cyclic Redundancy Check, cyclic redundancy check) check error, packet header and packet tail mismatch error, and meta frame length error;

在一种实施方式中,所述方法还包括:In one embodiment, the method also includes:

当宿端单板将从第一通道的缓存队列中读取的数据包进行输出后,如果所述第一通道出现告警,则将从第二通道的缓存队列中读取的数据包进行输出;After the sink board outputs the data packets read from the buffer queue of the first channel, if an alarm occurs in the first channel, output the data packets read from the buffer queue of the second channel;

在一种实施方式中,所述方法还包括:In one embodiment, the method also includes:

当所述第一通道告警恢复后,重新触发对所述第一通道的缓存队列写操作,以及对第一通道和第二通道的读缓存操作重新进行对齐处理。After the alarm of the first channel is recovered, the write operation to the buffer queue of the first channel is retriggered, and the read cache operation of the first channel and the second channel are re-aligned.

在一种实施方式中,所述每一个通道的缓存队列为FIFO(First Input FirstOutput,先入先出)队列。In one embodiment, the buffer queue of each channel is a FIFO (First Input First Output, First In First Out) queue.

实施例2Example 2

如图2所示,本发明实施例提供了一种数据保护装置,包括:As shown in Figure 2, an embodiment of the present invention provides a data protection device, including:

源端单板处理模块10,用于为原始数据包添加时间戳,并通过两个通道将添加时间戳后的数据包并行发送至宿端单板;The source-end single-

宿端单板处理模块20,用于在两个通道并行接收数据包,根据所述数据包携带的时间戳确定写入每一个通道的缓存队列的数据包并将所述数据包分别写入每一个通道的缓存队列中,从两个通道的缓存队列中并行读取数据包,根据所述数据包携带的时间戳对两个通道读取的数据包进行对齐处理,在对两个通道的读缓存操作对齐成功后,将从任意一个通道的缓存队列中读取的数据包进行输出。The sink-end single-

在一种实施方式中,所述数据包包括:时分复用TDM数据包;In one embodiment, the data packet includes: a time division multiplexed TDM data packet;

在一种实施方式中,所述源端单板处理模块,用于采用以下方式为原始数据包添加时间戳:在TDM数据包的包头添加时间戳;In one embodiment, the source-end single-board processing module is configured to add a time stamp to the original data packet in the following manner: add a time stamp to the header of the TDM data packet;

在一种实施方式中,所述两个通道均为Interlaken通道;In one embodiment, the two passages are Interlaken passages;

在一种实施方式中,所述宿端单板处理模块,用于采用以下方式根据所述数据包携带的时间戳确定写入每一个通道的缓存队列的数据包并将所述数据包分别写入每一个通道的缓存队列中:针对每一个通道,当所述通道接收到的数据包的时间戳从最大值变为最小值时,将接收携带所述最小值时间戳的数据包的时刻作为参考时刻,将在所述参考时刻之前接收的所有数据包写入该通道的缓存队列中;In one embodiment, the sink-end single-board processing module is configured to determine the data packets written into the cache queue of each channel according to the timestamp carried by the data packets in the following manner and write the data packets respectively into the buffer queue of each channel: for each channel, when the time stamp of the data packet received by the channel changes from the maximum value to the minimum value, the time when the data packet carrying the minimum value time stamp is received is taken as At a reference time, write all data packets received before the reference time into the buffer queue of the channel;

在一种实施方式中,所述宿端单板处理模块,用于采用以下方式根据所述数据包携带的时间戳对两个通道读取的数据包进行对齐处理:当两个通道的缓存队列中允许读取的数据包的数量均达到或超过读取阈值时,同时读取两个通道的缓存队列,当从两个通道的缓存队列中读取的前n个数据包携带的时间戳相同时,确定两个通道读取的数据包对齐;In one embodiment, the sink-end single-board processing module is configured to perform alignment processing on the data packets read by the two channels according to the timestamps carried by the data packets in the following manner: when the buffer queues of the two channels When the number of data packets allowed to be read in all reaches or exceeds the read threshold, the buffer queues of the two channels are read at the same time. When the timestamps carried by the first n data packets read from the buffer queues of the two channels are the same At the same time, determine the alignment of the data packets read by the two channels;

其中,n可以取值为1或2或3或其他数值;Wherein, n can take the value of 1 or 2 or 3 or other values;

在一种实施方式中,所述宿端单板处理模块,还用于采用以下方式根据所述数据包携带的时间戳对两个通道读取的数据包进行对齐处理:当一个通道的缓存队列中允许读取的数据包的数量达到或超过读取阈值,而另一个通道的缓存队列中允许读取的数据包的数量为零时,确定两个通道的读缓存操作不满足对齐条件;In one embodiment, the sink-end single-board processing module is further configured to perform alignment processing on the data packets read by two channels according to the timestamps carried by the data packets in the following manner: when the buffer queue of one channel When the number of data packets allowed to be read in reaches or exceeds the read threshold, and the number of data packets allowed to be read in the cache queue of another channel is zero, it is determined that the read cache operations of the two channels do not meet the alignment condition;

在一种实施方式中,所述宿端单板处理模块,用于采用以下方式根据所述数据包携带的时间戳确定写入每一个通道的缓存队列的数据包并将所述数据包分别写入每一个通道的缓存队列中:查询每一个通道的告警信息;对任意一个通道,在未查询到所述通道的告警信息时,触发对所述通道的写缓存处理;In one embodiment, the sink-end single-board processing module is configured to determine the data packets written into the cache queue of each channel according to the timestamp carried by the data packets in the following manner and write the data packets respectively Enter the cache queue of each channel: query the alarm information of each channel; for any channel, when the alarm information of the channel is not queried, trigger the write cache processing of the channel;

在一种实施方式中,所述宿端单板处理模块,还用于查询每一个通道的告警信息后,如果查询到任意一个通道的告警信息后,则对所述告警信息进行处理;In one embodiment, the sink-side single-board processing module is further configured to process the alarm information after querying the alarm information of each channel, if the alarm information of any channel is inquired;

所述告警信息包括以下至少一种:Interlaken通道未对齐、去偏移失败、CRC(Cyclic Redundancy Check,循环冗余校验)校验错误、包头和包尾不匹配错误、和元帧长度错误;The alarm information includes at least one of the following: Interlaken channel misalignment, de-skew failure, CRC (Cyclic Redundancy Check, cyclic redundancy check) check error, packet header and packet tail mismatch error, and meta frame length error;

在一种实施方式中,所述宿端单板处理模块,还用于将从第一通道的缓存队列中读取的数据包进行输出后,如果所述第一通道出现告警,则将从第二通道的缓存队列中读取的数据包进行输出;In one embodiment, the sink-side single-board processing module is further configured to output the data packets read from the buffer queue of the first channel, and if an alarm occurs on the first channel, output the data packets from the first channel The data packets read in the buffer queue of the second channel are output;

在一种实施方式中,所述所述宿端单板处理模块,还用于当所述第一通道告警恢复后,重新触发对所述第一通道的缓存队列写操作,以及对第一通道和第二通道的读缓存操作重新进行对齐处理。In one embodiment, the sink-side single-board processing module is further configured to re-trigger the write operation to the buffer queue of the first channel after the alarm of the first channel recovers, and Re-align with the read cache operation of the second channel.

示例1Example 1

如图4所示,本示例提供一种数据保护装置,包括:源端单板和宿端单板;所述源端单板包括:TDM包处理模块、第一通道发送模块、和第二通道发送模块;所述宿端单板包括:第一通道接收模块、第二通道接收模块、第一告警处理模块、第二告警处理模块、FIFO读写控制模块、第一FIFO模块、第二FIFO模块、和包输出模块;As shown in Figure 4, this example provides a data protection device, including: a source board and a sink board; the source board includes: a TDM packet processing module, a first channel sending module, and a second channel A sending module; the sink board includes: a first channel receiving module, a second channel receiving module, a first alarm processing module, a second alarm processing module, a FIFO read and write control module, a first FIFO module, and a second FIFO module , and the package output module;

所述TDM包处理模块,用于为原始TDM数据包添加时间戳,并将添加了时间戳的TDM数据包并行分发至第一通道发送模块和第二通道发送模块;The TDM packet processing module is used to add a time stamp to the original TDM data packet, and distribute the time stamped TDM data packet to the first channel sending module and the second channel sending module in parallel;

所述第一通道发送模块,用于将添加了时间戳的TDM数据包通过第一Interlaken通道发送至宿端单板;The first channel sending module is configured to send the time stamped TDM data packet to the sink board through the first Interlaken channel;

所述第二通道发送模块,用于将添加了时间戳的TDM数据包通过第二Interlaken通道发送至宿端单板;The second channel sending module is configured to send the TDM data packet with the time stamp added to the sink end single board through the second Interlaken channel;

第一通道接收模块,用于通过第一Interlaken通道接收TDM数据包,通知第一告警处理模块查询所述第一Interlaken通道是否存在告警信息;The first channel receiving module is used to receive the TDM packet through the first Interlaken channel, and notify the first alarm processing module to inquire whether there is alarm information in the first Interlaken channel;

第一告警处理模块,用于当查询到第一Interlaken通道的告警信息后,对所述告警信息进行处理,并通知FIFO读写控制模块;当未查询到第一Interlaken通道的告警信息时,通知FIFO读写控制模块第一Interlaken通道接口正常;The first alarm processing module is used to process the alarm information after inquiring about the alarm information of the first Interlaken channel, and notify the FIFO read and write control module; when not inquiring about the alarm information of the first Interlaken channel, notify The first Interlaken channel interface of the FIFO read-write control module is normal;

第二通道接收模块,用于通过第二Interlaken通道接收TDM数据包,通知第二告警处理模块查询所述第二Interlaken通道是否存在告警信息;The second channel receiving module is used to receive the TDM packet through the second Interlaken channel, and notifies the second alarm processing module to inquire whether there is alarm information in the second Interlaken channel;

第二告警处理模块,用于当查询到第二Interlaken通道的告警信息后,对所述告警信息进行处理,并通知FIFO读写控制模块;当未查询到第二Interlaken通道的告警信息时,通知FIFO读写控制模块第二Interlaken通道接口正常;The second alarm processing module is used to process the alarm information after inquiring about the alarm information of the second Interlaken channel, and notify the FIFO read and write control module; when not inquiring about the alarm information of the second Interlaken channel, notify The interface of the second Interlaken channel of the FIFO read-write control module is normal;

其中,所述告警信息可以包括以下至少一种:Interlaken通道未对齐、去偏移失败、CRC(Cyclic Redundancy Check,循环冗余校验)校验错误、包头和包尾不匹配错误、和元帧长度错误;Wherein, the alarm information may include at least one of the following: Interlaken channel misalignment, de-skew failure, CRC (Cyclic Redundancy Check, cyclic redundancy check) check error, packet header and packet tail mismatch error, and metaframe wrong length;

FIFO读写控制模块,用于获知第一Interlaken通道接口正常后,当所述第一Interlaken通道接收到的数据包的时间戳从最大值变为最小值时,将接收携带所述最小值时间戳的数据包的时刻作为参考时刻,触发第一FIFO模块写缓存;以及用于获知第二Interlaken通道接口正常后,当所述第二Interlaken通道接收到的数据包的时间戳从最大值变为最小值时,将接收携带所述最小值时间戳的数据包的时刻作为参考时刻,触发第二FIFO模块写缓存;The FIFO read and write control module is used to know that after the first Interlaken channel interface is normal, when the timestamp of the data packet received by the first Interlaken channel changes from a maximum value to a minimum value, it will receive and carry the minimum value timestamp The time of the data packet is used as a reference time to trigger the first FIFO module to write the buffer; and for knowing that the interface of the second Interlaken channel is normal, when the timestamp of the data packet received by the second Interlaken channel changes from the maximum to the minimum value, the moment of receiving the data packet carrying the minimum value timestamp is used as the reference moment to trigger the second FIFO module to write the cache;

第一FIFO模块,用于将在所述参考时刻之前接收的所有数据包写入第一Interlaken通道的FIFO缓存队列中;The first FIFO module is used to write all data packets received before the reference time into the FIFO buffer queue of the first Interlaken channel;

第二FIFO模块,用于将在所述参考时刻之前接收的所有数据包写入第二Interlaken通道的FIFO缓存队列中;The second FIFO module is used to write all data packets received before the reference time into the FIFO buffer queue of the second Interlaken channel;

FIFO读写控制模块,还用于查询第一Interlaken通道的FIFO缓存队列中允许读取的数据包的数量,以及查询第二Interlaken通道的FIFO缓存队列中允许读取的数据包的数量;当两个Interlaken通道的缓存队列中允许读取的数据包的数量均达到或超过读取阈值时,触发第一FIFO模块和第二FIFO模块同时读取FIFO缓存队列;当从两个Interlaken通道的FIFO缓存队列中读取的前n个数据包携带的时间戳相同时,通知包输出模块数据包对齐;当一个Interlaken通道的缓存队列中允许读取的数据包的数量达到或超过读取阈值,而另一个Interlaken通道的缓存队列中允许读取的数据包的数量为0时,确定两个Interlaken通道的读缓存操作不满足对齐条件;The FIFO read-write control module is also used to inquire about the quantity of data packets allowed to be read in the FIFO cache queue of the first Interlaken channel, and inquire about the quantity of the data packets allowed to be read in the FIFO cache queue of the second Interlaken channel; when two When the number of data packets allowed to be read in the buffer queues of two Interlaken channels reaches or exceeds the read threshold, the first FIFO module and the second FIFO module are triggered to read the FIFO buffer queues simultaneously; When the time stamps carried by the first n data packets read in the queue are the same, notify the packet output module that the data packets are aligned; When the number of data packets allowed to be read in the cache queue of an Interlaken channel is 0, it is determined that the read cache operations of the two Interlaken channels do not meet the alignment conditions;

包输出模块,用于在获知两个Interlaken通道的FIFO缓存队列读取的数据包对齐后,选择从第一Interlaken通道的FIFO缓存队列中读取的数据包进行输出,或者选择从第二Interlaken通道的FIFO缓存队列中读取的数据包进行输出;The packet output module is used to select the data packets read from the FIFO buffer queue of the first Interlaken channel to output after knowing that the data packets read by the FIFO buffer queues of the two Interlaken channels are aligned, or to select from the second Interlaken channel The data packets read in the FIFO buffer queue are output;

FIFO读写控制模块,还用于当选择从第一Interlaken通道的FIFO缓存队列中读取的数据包进行输出后,如果获知第一Interlaken通道出现告警,则选择从第二Interlaken通道的FIFO缓存队列中读取的数据包进行输出;当获知第一Interlaken通道告警恢复后,重新触发第一FIFO模块写缓存,以及重新控制第一FIFO模块和第二FIFO模块读缓存并进行数据包对齐处理。The FIFO read and write control module is also used to select the data packet read from the FIFO buffer queue of the first Interlaken channel for output, if it is learned that an alarm occurs in the first Interlaken channel, then select the FIFO buffer queue from the second Interlaken channel output the data packets read in; when the first Interlaken channel alarm is recovered, re-trigger the write buffer of the first FIFO module, and re-control the read buffer of the first FIFO module and the second FIFO module and perform data packet alignment processing.

在上述示例中,源端单板通过在原始数据包中添加时间戳为宿端单板的并行接收提供了数据对齐的参考依据。宿端单板在两个Interlaken通道并行接收数据包,根据所述数据包携带的时间戳对写缓存和读缓存的操作进行控制。在读缓存时,通过检查两个Interlaken通道读取的数据包携带的时间戳是否相同可以判断两个Interlaken通道读出的数据包是否对齐。当两个Interlaken通道的读操作对齐后,任意一个通道可以作为当前的工作通道,另一个通道可以作为备用通道。当工作通道发生故障时,由于两个通道读取的数据是一致的,因此可以达到无缝切换工作通道和备用通道,从而满足5G前传网络对通信延时和可靠性的苛刻要求。In the above example, the source board provides a data alignment reference for parallel reception of the sink board by adding a time stamp to the original data packet. The sink board receives the data packets in parallel on the two Interlaken channels, and controls the operations of the write cache and the read cache according to the timestamps carried in the data packets. When reading the cache, it can be judged whether the data packets read by the two Interlaken channels are aligned by checking whether the time stamps carried by the data packets read by the two Interlaken channels are the same. When the read operations of two Interlaken channels are aligned, any one channel can be used as the current working channel, and the other channel can be used as the standby channel. When the working channel fails, since the data read by the two channels is consistent, seamless switching between the working channel and the backup channel can be achieved, thereby meeting the stringent requirements of the 5G fronthaul network for communication delay and reliability.

本领域普通技术人员可以理解,上文中所公开方法中的全部或某些步骤、系统、装置中的功能模块/单元可以被实施为软件、固件、硬件及其适当的组合。在硬件实施方式中,在以上描述中提及的功能模块/单元之间的划分不一定对应于物理组件的划分;例如,一个物理组件可以具有多个功能,或者一个功能或步骤可以由若干物理组件合作执行。某些物理组件或所有物理组件可以被实施为由处理器,如中央处理器、数字信号处理器或微处理器执行的软件,或者被实施为硬件,或者被实施为集成电路,如专用集成电路。这样的软件可以分布在计算机可读介质上,计算机可读介质可以包括计算机存储介质(或非暂时性介质)和通信介质(或暂时性介质)。如本领域普通技术人员公知的,术语计算机存储介质包括在用于存储信息(诸如计算机可读指令、数据结构、程序模块或其他数据)的任何方法或技术中实施的易失性和非易失性、可移除和不可移除介质。计算机存储介质包括但不限于RAM、ROM、EEPROM、闪存或其他存储器技术、CD-ROM、数字多功能盘(DVD)或其他光盘存储、磁盒、磁带、磁盘存储或其他磁存储装置、或者可以用于存储期望的信息并且可以被计算机访问的任何其他的介质。此外,本领域普通技术人员公知的是,通信介质通常包含计算机可读指令、数据结构、程序模块或者诸如载波或其他传输机制之类的调制数据信号中的其他数据,并且可包括任何信息递送介质。Those of ordinary skill in the art can understand that all or some of the steps in the methods disclosed above, the functional modules/units in the system, and the device can be implemented as software, firmware, hardware, and an appropriate combination thereof. In a hardware implementation, the division between functional modules/units mentioned in the above description does not necessarily correspond to the division of physical components; for example, one physical component may have multiple functions, or one function or step may be composed of several physical components. Components cooperate to execute. Some or all of the physical components may be implemented as software executed by a processor, such as a central processing unit, digital signal processor, or microprocessor, or as hardware, or as an integrated circuit, such as an application-specific integrated circuit . Such software may be distributed on computer readable media, which may include computer storage media (or non-transitory media) and communication media (or transitory media). As known to those of ordinary skill in the art, the term computer storage media includes both volatile and nonvolatile media implemented in any method or technology for storage of information, such as computer readable instructions, data structures, program modules, or other data. permanent, removable and non-removable media. Computer storage media includes, but is not limited to, RAM, ROM, EEPROM, flash memory or other memory technology, CD-ROM, digital versatile disk (DVD) or other optical disk storage, magnetic cartridges, tape, magnetic disk storage or other magnetic storage devices, or can Any other medium used to store desired information and which can be accessed by a computer. In addition, as is well known to those of ordinary skill in the art, communication media typically embodies computer readable instructions, data structures, program modules, or other data in a modulated data signal such as a carrier wave or other transport mechanism, and may include any information delivery media .

需要说明的是,本发明还可有其他多种实施例,在不背离本发明精神及其实质的情况下,熟悉本领域的技术人员可根据本发明作出各种相应的改变和变形,但这些相应的改变和变形都应属于本发明所附的权利要求的保护范围。It should be noted that the present invention can also have other various embodiments, without departing from the spirit and essence of the present invention, those skilled in the art can make various corresponding changes and deformations according to the present invention, but these Corresponding changes and deformations should belong to the scope of protection of the appended claims of the present invention.

Claims (8)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201811573811.5A CN111355549B (en) | 2018-12-21 | 2018-12-21 | Data protection method and device |

| PCT/CN2019/127322 WO2020125792A1 (en) | 2018-12-21 | 2019-12-23 | Data output method and apparatus, and storage medium and device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201811573811.5A CN111355549B (en) | 2018-12-21 | 2018-12-21 | Data protection method and device |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN111355549A CN111355549A (en) | 2020-06-30 |

| CN111355549B true CN111355549B (en) | 2023-05-02 |

Family

ID=71100220

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201811573811.5A Active CN111355549B (en) | 2018-12-21 | 2018-12-21 | Data protection method and device |

Country Status (2)

| Country | Link |

|---|---|

| CN (1) | CN111355549B (en) |

| WO (1) | WO2020125792A1 (en) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN112713963A (en) * | 2020-12-16 | 2021-04-27 | 北京华环电子股份有限公司 | Signal nondestructive protection method and device, signal receiver and readable storage medium |

| CN113784118A (en) * | 2021-09-14 | 2021-12-10 | 广州博冠信息科技有限公司 | Video quality evaluation method and device, electronic equipment and storage medium |

| CN113965391B (en) * | 2021-10-27 | 2023-10-20 | 成都数默科技有限公司 | Method for bubble sorting of multi-data packet files |

| CN115017192B (en) * | 2022-05-23 | 2025-03-18 | 广东人工智能与先进计算研究院 | Voltage sequence data caching method and system |

| CN115022658B (en) * | 2022-05-30 | 2023-09-08 | 广州力加贺电子科技有限公司 | Method, device, equipment and medium suitable for embedded live broadcast data processing |

| CN116668985B (en) * | 2023-06-25 | 2024-09-10 | 成都飞机工业(集团)有限责任公司 | Low bit error rate method for wireless transmission of multi-source multi-node acquisition sensing data |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101873186A (en) * | 2009-04-22 | 2010-10-27 | 华为技术有限公司 | Method, station and system for compensation of transmission delay deviation between synchronous transmission channels |

| CN105379220A (en) * | 2013-03-18 | 2016-03-02 | 吉林克斯公司 | Timestamp correction in a multi-lane communication link with skew |

| WO2017202084A1 (en) * | 2016-05-25 | 2017-11-30 | 中兴通讯股份有限公司 | Network processor, network processing method and system, single board, and computer storage medium |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103684651B (en) * | 2012-09-13 | 2018-02-13 | 中兴通讯股份有限公司 | The fixed bit rate interface data method of reseptance and device of optical transfer network mixed service |

| US9461837B2 (en) * | 2013-06-28 | 2016-10-04 | Altera Corporation | Central alignment circutry for high-speed serial receiver circuits |

| US10536357B2 (en) * | 2015-06-05 | 2020-01-14 | Cisco Technology, Inc. | Late data detection in data center |

-

2018

- 2018-12-21 CN CN201811573811.5A patent/CN111355549B/en active Active

-

2019

- 2019-12-23 WO PCT/CN2019/127322 patent/WO2020125792A1/en not_active Ceased

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101873186A (en) * | 2009-04-22 | 2010-10-27 | 华为技术有限公司 | Method, station and system for compensation of transmission delay deviation between synchronous transmission channels |

| CN105379220A (en) * | 2013-03-18 | 2016-03-02 | 吉林克斯公司 | Timestamp correction in a multi-lane communication link with skew |

| WO2017202084A1 (en) * | 2016-05-25 | 2017-11-30 | 中兴通讯股份有限公司 | Network processor, network processing method and system, single board, and computer storage medium |

Also Published As

| Publication number | Publication date |

|---|---|

| CN111355549A (en) | 2020-06-30 |

| WO2020125792A1 (en) | 2020-06-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN111355549B (en) | Data protection method and device | |

| US9209922B2 (en) | Lossless adjustment method of ODUflex channel bandwidth and ODUflex channel | |

| US9025467B2 (en) | Hitless protection for traffic received from 1+1 protecting line cards in high-speed switching systems | |

| CN114172604A (en) | Time delay compensation method, device, equipment and computer readable storage medium | |

| KR20210038959A (en) | Service transmission method, equipment and computer storage medium | |

| US9722723B2 (en) | Dynamic hitless ODUflex resizing in optical transport networks | |

| EP1671444A1 (en) | Data mirroring system | |

| US20150016245A1 (en) | Method and apparatus for protection switching in packet transport system | |

| JP5195557B2 (en) | Data processing apparatus and non-instantaneous switching method | |

| US20090003235A1 (en) | Method and Apparatus For Data Frame Transmission | |

| WO2021139692A1 (en) | Clock port attribute recovery method, device, and system | |

| CN114301852B (en) | Message transmission control, generation and transmission methods, message transmission configuration methods, message transmission control, generation and transmission configuration equipment and message transmission configuration medium | |

| CN112073319B (en) | Path switching method and system | |

| CN116567455B (en) | A bandwidth adjustment method and apparatus | |

| CN110557268A (en) | Method and device for controlling transmission of Ethernet frames | |

| CN100474815C (en) | Method for adjusting link capacity | |

| CN119544435A (en) | Clock determination method, device, equipment, system and storage medium | |

| CN114339482B (en) | Path switching methods, devices and systems, electronic devices, storage media | |

| CN115225984B (en) | Data processing method, device and system in optical network | |

| CN118900290B (en) | Message processing methods, apparatus, devices and readable storage media | |

| CN120186053A (en) | Channel detection method, device, equipment and computer readable storage medium | |

| WO2025161868A1 (en) | Code block processing method and apparatus, device, system, storage medium and program product | |

| CN121644329A (en) | Data synchronization method, standby device, main device and control unit | |

| CN118843026A (en) | Alarm detection device of OSU | |

| CN120614089A (en) | Data transmission method, device, equipment, system, storage medium and program product |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| GR01 | Patent grant | ||

| GR01 | Patent grant |